Digital and Computer System [3] - Programmable Logic Devices, Factual Stuffs

Programmable Logic Devices (PLD)

Types of PLDs:

- Read-only memory

- PLA - Programmable Logic Array

- PAL - Programmable Array Logic

| Symbol | Stands for |

|---|---|

| P | Programmable |

| F | Fixed |

Read-only memory

Depending on the programming technology and approaches, read-only memories have different names:

- ROM – mask programmed (programmed in manufacturing stage)

- PROM – fuse or antifuse programmed (After you programmed it, you cannot change it)

- EPROM – erasable floating gate programmed (use UV to erase it)

- EEPROM – electronically erasable floating gate programmed (use higher voltage to erase it)

- FLASH – electrically erasable floating gate with multiple erasure and programming modes

ROM

- A ROM having n address pins can store 2n words.

- A particular word is selected and output when an address is provided to the ROM.

- No. of address pins determines the max. No. of input variables of a function that can be supported.

- No. of data pins (word length) determines the max. No. of functions that can be supported.

Examples with ROM

PLA (Programmable Logic Array)

The decoder is replaced by an array of AND gates that can be programmed to generate product terms of the input variables.

PLA implements SOP or complimented SOP functions.

The size of a PLA is specified by the number of inputs, the number of product terms, and the number of outputs.

Examples with PLA (Requires Kmap)

Note :

A careful investigation must be undertaken in order to reduce the number of distinct product terms.

The number of literals in a term is less important.

Should share terms between the outputs to reduce the product terms (complexity).

PAL (Programmable Array Logic)

Only AND gates are programmable and product terms can’t be shared by multiple functions Design for the PAL device is easier, but is not as flexible as that for the PLA.

Since number of products is limited for each OR gate, outputs can be fed back into the inputs of the AND gates through programmed connections to improve the flexibility.

Should minimize the number of cascade stages to minimize the output delay.

Should minimize the connections to lower the power consumption.

How to make it?

Minimize number of products -> needs fewer cascade stages and less connections.

Minimize lateral cost of each product -> needs less connections.

1 Input Gate = 1 Unit Delay

Example with PAL (Not Require Kmap)

Introduction to the microprocessor and computer

Composition of a Computer System

CPU

Central Processing Unit (CPU) contains:

- Arithmetic logic unit (ALU) - contains electrical circuits that carry out each instruction

- Registers - store data or instructions that are needed immediately or frequently

- Control Unit (CU)

- Control movement of data to and from CPU registers and other hardware components.

- Access program instructions and issue appropriate commands to the ALU.

System bus

A bus is a shared electrical or optical channel that connect two or more devices.

A system bus is the main channel for moving data and instructions to and from hardware components.

Its capacity (bandwidth) is a critical factor in computer performance. (the higher the better)

Two busses with different capacities (bandwidths) can be connected if we place a controller (called a bridge) between them.

Primary Storage

Contains millions or billions of storage locations.

Secondary Storage

is composed of high-capacity nonvolatile storage.

Comparison of storage types

| Storage type | Implementation | Content | Typical quantity |

|---|---|---|---|

| CPU registers | High-speed electrical devices in the CPU | Currently executing instructions and associated data inputs and outputs | Several dozen to a few hundred instructions and data items |

| Primary Storage | High-speed electrical devices (RAM) outside but close to the CPU | Currently running programs and data needed immediately (if they fit in primary storage) | 1-8 billion data items per GPU |

| Secondaty Storage | Low-speed electromagnetic and optical devices | Programs not currently running and data not currently being accessed by programs | Brillions, trillions, quadrillions of data items |

I/O devices

The variety of I/O devices in modern computers addresses the many different forms of human-to-computer and computer-to-computer communication.

I/O devices can be classified broadly into human-oriented and computer- oriented communication devices.

Computer system classification

Microcomputer a.k.a. personal computer (PC)

- a computer system designed to meet a single user’s information processing

Minicomputer

- designed to provide information processing for multiple users and run many application programs simultaneously.

Mainframe computer system

- handles the information-processing needs of a large number of users and applications

Supercomputer

- designed for one purpose rapid mathematical computation

Server (based on the mode of use)

- a computer system that manages shared resources, such as file systems, databases, Web sites, printers, and high-speed CPUs, and allows users to access these resources over a local or wide area network.

Cluster

- a group of similar or identical computers, connected by a high-speed network, that cooperate to provide services or run a single application.

Grid

- a group of dissimilar computers, connected by a high-speed network, that cooperate to provide services or run a shared application.

A Typical System should have:

- Display

- Motherboard

- CPU(Microprocessor)

- Primarystorage(RAM)

- Expansioncards

- Powersupply

- Optical disc drive

- Hard disk drive (HDD)

- Keyboard

- Mouse

microprocessor

- an IC containing all the circuits and connections that implement a CPU.

From a microprocessor’s perspective,

- Microprocessor = CPU

- A computer system is constructed with CPU, memory system and I/O system.

- CPU is the center of a computer system

The Memory and I/O systems

Each memory location is associated with a memory address.

A CPU accesses a memory location with the address bus.

The width of the address bus (in terms of bits) defines how many memory locations that a CPU can access theoretically.

This theoretical number of locations (in terms of bytes) forms the memory space of the system.

The real number of accessible memory location is subject to physical constraints (e.g. whether it exists or not.).

A memory map tells

- How the memory space is divided into a number of portions

- Which portion is used for what purpose

Each port is associated with a port address.

A CPU accesses a port with the address bus.

This theoretical number of ports (each of which can deliver 1 byte at a time) forms the I/O space of the system.

The real number of accessible port is subject to physical constraints (e.g. whether there is a real device connected to the port.).

The Microprocessor

The microprocessor performs 3 main tasks for the computer system:

- data transfer between itself and the memory or I/O systems,

- simple arithmetic and logic operations, and

- program flow via simple decisions.

Its power is in its ability to execute millions of instructions per second from a program and make simple decisions.

Buses

A bus is a common group of wires that interconnect components in a computer system.

Buses are used to transfer address, data and control information between the microprocessor and its memory and I/O devices.

The microprocessor and its architecture

Basic CPU Architecture

Operation -register,hex(address)

ADD AX,[2000]

MOV BX,AX <- move AX content into BX content

ALU (Arithmetic Logic Unit)

-

Takes operand(s) on the inputs (A and B) and produces a result on the output (Y).

-

Performs logical and arithmetic operations -

-

including add, subtract, and, or, not, shift right, shift left and others.

Register File

- is a set of storage locations (registers) for storing temporary results.

- Size varies from CPU to CPU.

Instruction Register

- Store the instruction currently being executed by the processor

Control Unit

- Decodes the instruction in the instruction register

- Sets signals which control the operation of most other units of the processor and even external devices

Program counter

- Holds the memory address of the next instruction to be executed.

- Is automatically updated every instruction cycle to point to the next instruction in the program.

Memory Address Register

- loaded with the address of the next data word to be fetched from or stored into main memory.

Address Bus

- Used to transfer addresses to memory and memory-mapped peripherals.

- Driven by the processor acting as a bus master.

Data Bus

- Carries data to and from the processor, memory and peripherals.

- Driven by the source of data, i.e. processor, memory or peripheral device.

Control Bus

- Used to deliver control signals from the Control unit

System performance

Clock rate

-

System clock:

a digital circuit that generates timing pulses, or signals, and transmits the pulses to other devices in the computer.

-

Expressed in hertz(Hz)

CPU cycle time = 1/(CPU’s clock rate).

CPU performance consideration

- Is not based on clock rate but the rate at which instructions are executed.

- On MIPS or MFLOPS

- MIPS (millions of instructions per second) for manipulating single-precision integers.

- MFLOPS (millions of floating-point operations per second) for manipulating single-precision floating-point numbers.

- effective MIPS rate << computed MIPS rate of the CPU measured in isolation because of delays imposed by waiting for storage and I/O devices.

Benchmarks

A benchmark is a measure of CPU or computer system performance when carrying out one or more specific tasks.

Instruction set architecture

An instruction set, or instruction set architecture (ISA) is the part of the computer architecture related to programming. including the native

- data types

- instructions,

- registers,

- addressing modes,

- memory architecture,

- interrupt and exception handling, and

- external I/O

Internal microprocessor architecture

Before a program is written or any instruction is investigated, the internal configuration of the microprocessor must be known.

S stands for Segment

Classification of registers:

- Visible/invisible

- General purpose/special purpose

Program visible/invisible

Program visible registers:

- are used during programming and specified by the instructions.

Program invisible registers:

- can not be addressable directly during applications programming but may be used indirectly during system programming are considered.

General/Special-purpose

Some registers are general-purpose or multipurpose registers, while some have special purposes.

Multi-purpose registers:

- hold various data sizes (bytes, words, or doublewords)

- are used for almost any purpose as dictated by a program

- But sometimes are used for some special purposes.

BP stand for base pointer

DI stand for Destination Index

SI stand for Source Index

Real mode memory addressing

In real mode operation, it allows an Intel CPU to address only the first 1M byte of memory space (even the Pentium microprocessor).

Real mode operation

- Allows downward compatibility

- Is the default operation mode

Segments and offsets

A combination of a segment address and an offset address access a memory location in the real mode.

The segment address, located within one of the segment registers, defines the beginning address of any 64K-byte memory segment.

The offset address selects any location within the 64K-byte memory segment.

Size of a segment = 64K bytes

Default segment and offset

The microprocessors has a set of rules that apply to segments whenever memory is addressed.

These rules, which apply in either the real or protected mode, define the segment register and offset register combination used by certain addressing modes.

CS - code segment register

- defines the start of the code segment

IP - instruction pointer

- locates the next instruction within the code segment

Stack data are references through the stack segment at the memory location addressed by either the stack pointer (SP) or the base pointer (BP).

Relocation

Segment and offset addressing scheme allows relocation.

A relocatable program is one that can be placed into any area of memory and executed without change.

Relocatable data are data that can be placed in any area of memory and used without any change to the program.

Memory is addressed within a segment by an offset address.

Instructions and addressing modes

Basic Computer Operation Cycle

A program is a sequence of instructions supported by the ISA of a microprocessor.

Instructions are fetched from the memory and executed one by one.

Types of Instructions

- Processor-memory - transfer data between processor and memory

- Processor-I/O - data transferred to or from a peripheral device

- Data processing - arithmetic or logic operation on data

- Control - alter sequence of execution

What is a instruction cycle?

- the time period spent for executing an instruction

- The exact time duration varies from instruction to instruction

Basically :

- Fetch the instruction from memory into a control register

- Decode the instruction

- Locate the operands used by the instruction

- Fetch operands from memory (if necessary)

- Execute the operation in processor register

- Store the results in the proper place

- Go back to step 1 to fetch the next instruction

Addressing Modes

(WILL NOT BE COVERED IN THIS COMMING EXAM THEREFORE LEAVE IT BLANK FOR A WHILE)

Bonus : Logic Circuit (Lab Tool)

Components That you must know how to use

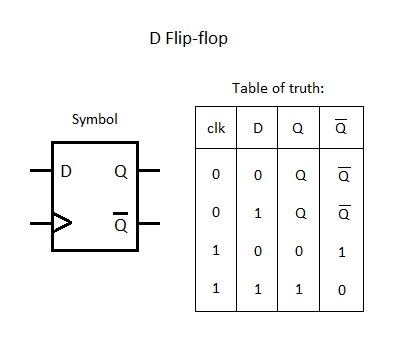

D Flip Flop

Data = input, Q = ouput (which is Data). Q’ means .

3-bit Counter

When reset = 1, the right counter back to 000. Otherwise, the counter loops from 000 to 111.

SR latch

Data = input, Q = ouput (which is Data). Q’ means .